VSCLAB introduce hybrid temporal computing framework for power efficient AI computing

VSCLAB is excited to share that we proposed a new low-power computing paradigm called Hybrid Temporal Computing (HTC). In HTC, data for multiplication are encoded in a hybrid format combining temporal data and traditional bitstream data. The temporal data concept is inspired by recently proposed temporal computing (or race logic), where information is encoded as time delays or waveforms. Temporal computing can significantly reduce energy consumption, as it requires only a single switch to represent data transition but with limited applications due to waveform restrictions.

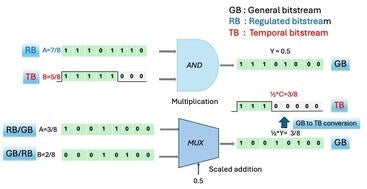

The illustration below demonstrates how HTC handles multiplication and addition efficiently. Our initial findings indicate that HTC can achieves remarkable power savings compared to state-of-the-art stochastic computing methods, with small accuracy trade-offs in applications such as DCT/iDCT and digital filter accelerators.

This work will be published in coming ASPDAC’25!

Please see the linked post here